i. sample.py

ii. design_1_wrapper.xsa

iii. hello_world.elf

!NOTE: file name might vary

2. Sample contents of sample.py

import xsdb

import time

# required files

platform_file = "design_1_wrapper.xsa"

bitstream_file = platform_file.split(".")[0] + ".bit"

elf_file = "hello_world.elf"

# start session

session = xsdb.start_debug_session()

# connect to hw_server (can be run as: C:\Xilinx\Vitis\2024.1\bin\unwrapped\win64.o\.\hw_server.exe)

session.connect(url="tcp:127.0.0.1:3121")

# set JTAG target

targets = session.targets()

print(targets)

jtag_target = session.targets("--set", filter="name =~ xc7a35t")

# # download bitstream

# jtag_target.fpga(file="top_running_lights.bit")

# open hardware design

jtag_target.loadhw("--regs", hw=platform_file)

jtag_target.fpga(file=bitstream_file)

time.sleep(3)

# set target

hart_target = session.targets("--set", filter="name =~ *Hart*")

# download ELF to target

hart_target.dow(elf_file)

time.sleep(3)

hart_target.rst()

# disconnect to hw_server

#hart_target.stop()

#jtag_target.stop()

session.disconnect()

2. Create a file named fpga-slurm.sbatch

Make sure the files in [1] are in the same folder as fpga-slurm.sbatch

Copy the following format, change sample.py to your python file:

#!/bin/bash

#SBATCH --job-name=fpga-test

#SBATCH --gres=gpu:1 # request 1 FPGA

#SBATCH --gres=gpu:1 # request 1 FPGA

#SBATCH --output=fpga_out_%j.txt

source /opt/Vitis/2024.1/settings64.sh

vitis_run sample.py # Change sample.py to your python file.

#sleep 300 # Uncomment this line if you need to access FGPA for 5 minutes

echo "Job finished." #

2. Open Terminal, then type:

sbatch fpga-slurm.sbatch

3. Take note of the batch job id

juan.dela.cruz@student-vm-coe168:~$ sbatch testfpgaslurm.sbatch

juan.dela.cruz@student-vm-coe168:~$ sbatch testfpgaslurm.sbatch

Submitted batch job 104

4. Check the status of you job by typing

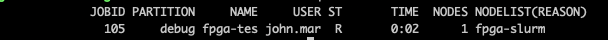

juan.dela.cruz@student-vm-coe168:~$ squeue

5. Wait for the job to finish. To view the result of the finished job, open the file: fpga_out_%j.txt

6. If you wish to cancel your existing job:

juan.dela.cruz@student-vm-coe168:~$ scancel <job ID>